# 1Kx8STATICRAM

# MK4118(P/N)Series

## **FEATURES**

☐ Address Activated TM Interface combines benefits of Edge Activated TM and fully static.

□ High performance

| Part number | Access time | Cycle time |

|-------------|-------------|------------|

| MK4118-1    | 120 nsec    | 120 nsec   |

| MK4118-2    | 150 nsec    | 150 nsec   |

| MK4118-3    | 200 nsec    | 200 nsec   |

| MK4118-4    | 250 nsec    | 250 nsec   |

☐ Single +5 volt power supply

☐ TTL compatible I/O

Fanout:

2 - Standard TTL

2 - Schottky TTL

12 - Low power Schottky TTL

□ Low Power - 400mw Active

☐ 24-pin ROM/PROM compatible pin configuration

☐ CS, OE, and LATCH functions for flexible system operation

□ Read-Modify-Write Capability

#### DESCRIPTION

The MK4118 uses MOSTEK's Poly R N-Channel Silicon Gate process and advanced circuit design techniques to package 8192 bits of static RAM on a single chip. MOSTEK's address activated TM circuit design technique is utilized to achieve high performance, low power, and easy user implementation. The device has a V<sub>IH</sub> = 2.2, V<sub>IL</sub> = 0.8V, V<sub>OH</sub> = 2.4, V<sub>OL</sub> = 0.4V making it totally compatible with all TTL family devices.

The MK4118 is designed for all wide word memory applications. The MK4118 provides the user with a

high-density, cost-effective 1Kx8 bit Random Access Memory. Fast Output Enable ( $\overline{OE}$ ) and Chip Select ( $\overline{CS}$ ) controls are provided for easy interface in microprocessor or other bus-oriented systems. The MK4118 features a flexible Latch ( $\overline{L}$ ) function to permit latching of the address and  $\overline{CS}$  status at the user's option. Common data and address bus operation may be performed at the system level by utilizing the  $\overline{L}$  and  $\overline{OE}$  functions for the MK4118. The latch function may be bypassed by merely tying the latch pin to VCC, providing fast ripple-through operation.

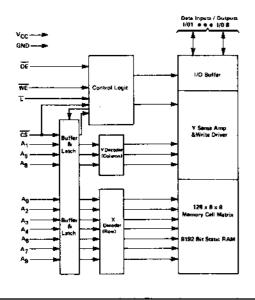

# **BLOCK DIAGRAM**

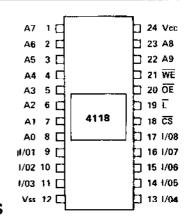

# **PIN OUT**

# **PIN NAMES**

| A0 - A9 | Address Inputs |

|---------|----------------|

| CS      | Chip Select    |

| Vss     | Ground         |

| Vcc     | Power (+5V)    |

|         |                |

WE Write Enable

OE Output Enable

L Latch

1/01 1/08 Data In/

Data Out Port

## **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to VSS      | <b>–0.5V</b> to +7.0V   |

|-----------------------------------------|-------------------------|

| Operating Temperature TA (Ambient)      | $\dots$ 0° C to + 70° C |

| Storage Temperature (Ambient) (Ceramic) | . –65°C to +150°C       |

| Storage Temperature (Ambient) (Plastic) | . –55° C to +125° C     |

| Power Dissipation                       | 1 Watt                  |

| Short Circuit Output Current            | 20mA                    |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ} C \leq T_{A} \leq +70^{\circ} C)$

|     | PARAMETER                    | MIN  | TYP | MAX  | UNITS | NOTES |

|-----|------------------------------|------|-----|------|-------|-------|

| VCC | Supply Voltage               | 4,75 | 5.0 | 5.25 | Volts | 1     |

| VSS | Supply Voltage               | 0    | 0   | 0    | Volts | 1     |

| VIH | Logic "1" Voltage All Inputs | 2.2  |     | 7.0  | Volts | 1     |

| VIL | Logic "0" Voltage All Inputs | -0.3 |     | 0.8  | Volts | 1     |

# DC ELECTRICAL CHARACTERISTICS1

$(0^{\circ}C \le T_{A} \le +70^{\circ}C) \text{ (V}_{CC} = 5.0 \text{ volts} \pm 5\%)$

|     | PARAMETER                                              | MIN | MAX | UNITS | NOTES |

|-----|--------------------------------------------------------|-----|-----|-------|-------|

| CC1 | Average V <sub>CC</sub> Power Supply Current (Active)  |     | 80  | mA    |       |

| CC2 | Average V <sub>CC</sub> Power Supply Current (Standby) |     | 60  | mA    |       |

| IL  | Input Leakage Current (Any Input)                      | -10 | 10  | μΑ    | 2     |

| loL | Output Leakage Current                                 | -10 | 10  | μΑ    | 2     |

| Vон | Output Logic "1" Voltage IOUT=-1mA                     | 2.4 |     | Volts |       |

| VOL | Output Logic "O" Voltage IOUT= 4mA                     |     | 0.4 | Volts |       |

# AC ELECTRICAL CHARACTERISTICS1

$(0^{\circ} C \le T_{A} \le + 70^{\circ} C) (V_{CC} = + 5.0 \text{ volts } \pm 5\%)$

| -                | PARAMETER                          | TYP  | MAX | NOTES |

|------------------|------------------------------------|------|-----|-------|

| CI               | Capacitance on all pins except I/0 | 4pF  |     |       |

| C <sub>I/0</sub> | Capacitance on I/O pins            | 10pF |     |       |

NOTES:

#### **OPERATION**

# **READ MODE**

The MK4118 is in the READ MODE whenever the Write Enable control input ( $\overline{WE}$ ) is in the high state. The state of the 8 data I/O signals is controlled by the Chip Select ( $\overline{CS}$ ) and Output Enable ( $\overline{OE}$ ) control signals. The READ MODE memory cycle may be either ASYNCHRONOUS (ripple-through) or SYNCHRONOUS, depending on user control of the Latch Input Signal ( $\overline{L}$ ).

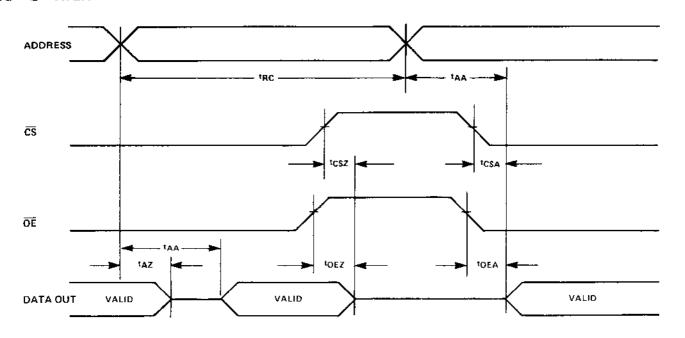

#### **ASYNCHRONOUS READ CYCLE**

In the ASYNCHRONOUS READ CYCLE mode of operation, the MK4118 provides a fast address ripple-through access of data from 8 of 8192 locations in the static storage array. Thus, the unique address specified by the 10 Address Inputs (An) define which 1 of 1024 bytes of data is to be accessed. The ASYNCHRONOUS READ CYCLE is defined by  $\overline{\text{WE}} = \overline{\text{L}} = \text{High}$ .

All voltages referenced to V<sub>SS</sub>.

<sup>2.</sup> Measured with 0 ≤ V<sub>1</sub> ≤5V and outputs deselected

# **ELECTRICAL CHARACTERISTICS**

$(0^{\circ}\text{C} \leq \text{TA} \leq 70^{\circ}\text{C} \text{ and } \text{V}_{\text{CC}} = 5.0 \text{ volts } \pm 5\%)$

| SYMBOL           | PARAMETER                    |     | MK4118-1 |     | MK4118-2 |     | MK4118-3 |     | MK4118-4 |      | NOTE |

|------------------|------------------------------|-----|----------|-----|----------|-----|----------|-----|----------|------|------|

|                  |                              | MIN | MAX      | MIN | MAX      | MIN | MAX      | MIN | MAX      |      |      |

| tRC              | Read Cycle Time              | 120 |          | 150 |          | 200 |          | 250 |          | ns   |      |

| tAA              | Address Access Time          |     | 120      |     | 150      |     | 200      |     | 250      | ns   | -    |

| <sup>t</sup> CSA | Chip Select Access Time      |     | 60       |     | 75       |     | 100      |     | 125      | ns   |      |

| tCSZ             | Chip Select Data Off Time    | 0   | 60       | 0   | 75       | 0   | 100      | 0   | 125      | ns   |      |

| <sup>t</sup> OEA | Output Enable Access Time    |     | 60       |     | 75       |     | 100      |     | 125      | ns   |      |

| <sup>t</sup> OEZ | Output Enable Data Off Time  | 0   | 60       | 0   | 75       | 0   | 100      | 0   | 125      | ns   |      |

| †AZ              | Address Data Off Time        | 10  |          | 10  |          | 10  |          | 10  |          | ns   |      |

| <sup>t</sup> ASL | Address To Latch Setup Time  | 0   |          | 0   |          | 0   |          | 0   |          | ns   |      |

| <sup>t</sup> AHL | Address From Latch Hold Time | 40  |          | 50  |          | 65  |          | 80  |          | ПŜ   |      |

| tCSL             | CS To Latch Setup Time       | 0   |          | 0   |          | 0   |          | 0   |          | ns   |      |

| †CHL             | CS From Latch Hold Time      | 40  |          | -50 |          | 65  |          | 80  |          | ns   |      |

| tLA              | Latch Off Access Time        |     | 160      |     | 200      |     | 260      |     | 325      | ns . |      |

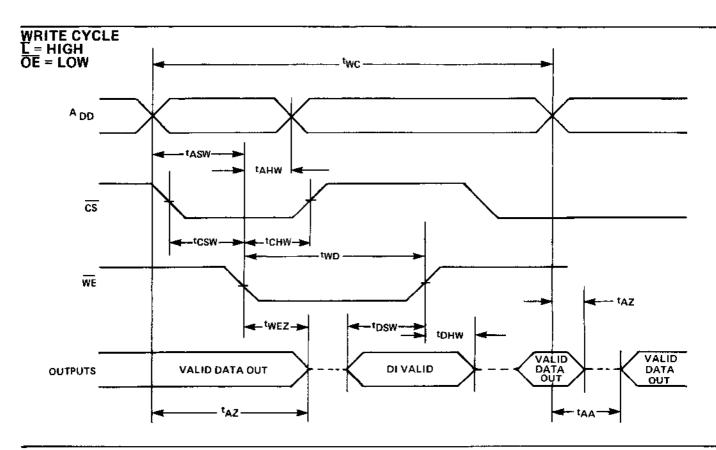

| twc              | Write Cycle Time             | 120 |          | 150 |          | 200 |          | 250 |          | ns   |      |

| †ASW             | Address To Write Setup Time  | 0   |          | 0   |          | 0   |          | 0   |          | ns   |      |

| tAHW             | Address From Write Hold Time | 40  |          | 50  |          | 65  |          | 80  |          | ns   |      |

| tCSW             | CS To Write Setup Time       | 0   |          | 0   |          | 0   |          | 0   |          | ns   |      |

| tCHW             | CS From Write Hold Time      | 40  |          | 50  |          | 65  |          | 80  |          | ns   |      |

| tDSW             | Data To Write Setup Time     | 20  | -        | 30  |          | 40  |          | 50  |          | ns   |      |

| tDHW             | Data From Write Hold Time    | 20  |          | 30  |          | 40  |          | 50  |          | ns   |      |

| twD              | Write Pulse Duration         | 50  |          | 70  |          | 95  |          | 120 |          | ns   |      |

| <sup>t</sup> LDH | Latch Duration, High         |     | DC       |     | DC       |     | DC       |     | DC       | ns   |      |

| <sup>t</sup> LDL | Latch Duration, Low          |     | DC       |     | DC       |     | DC       |     | DC       | пѕ   | _    |

| <sup>t</sup> WEZ | Write Enable Data Off Time   | 0   | 60       | 0   | 75       | 0   | 100      | 0   | 125      | กร   |      |

| t <sub>L</sub> Z | Latch Data Off Time          | 10  |          | 10  |          | 10  | :        | 10  | :        | ns   |      |

# ASYNCHRONOUS READ CYCLE (Cont'd)

A transition on any of the 10 address inputs will disable the 8 Data Output Drivers after  $t_{AZ}$ . Valid Data will be available to the 8 Data Output Drivers within  $t_{AA}$  after all address input signals are stable, and the data will be output under control of the Chip Select  $(\overline{CS})$  and Output Enable  $(\overline{OE})$  signals.

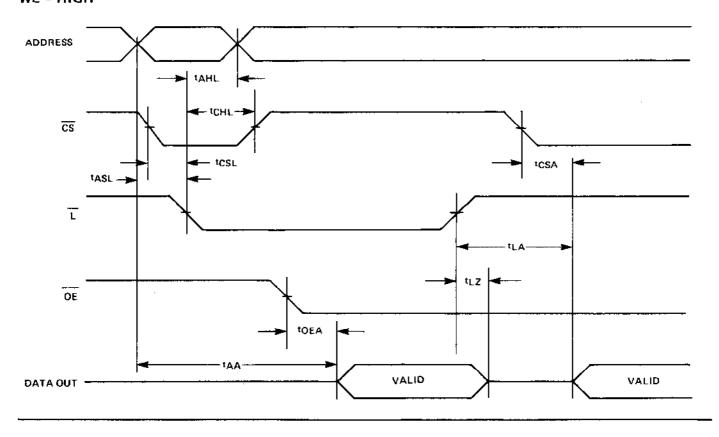

#### SYNCHRONOUS READ CYCLE

The SYNCHRONOUS READ CYCLE is also defined by the Write Enable control input (WE) being in the high state, and it is synchronized by proper control of the Latch (L) input.

As the Latch control input  $(\overline{L})$  is taken low, Address (An) and Chip Select  $(\overline{CS})$  inputs that are stable for the specified set-up and hold times are latched internally. Data out corresponding to the latched address

will be supplied to the Data Output drivers. The output drivers will be enabled to drive the Output Data Bus under control of the Output Enable  $(\overline{OE})$  and latched Chip Select  $(\overline{CS})$  inputs.

Taking the latch input high begins another read cycle for the memory locations specified by the address then appearing on the Address Input (An). Returning the latch control to the low state latches the new Address and Chip Select inputs internally for the remainder of the SYNCHRONOUS READ CYCLE.

# WRITE MODE

The MK4118 is in the WRITE MODE whenever the Write Enable (WE) and Chip Select (CS) control inputs are in the low state. The status of the 8 output buffers during a write cycle is expalined below.

# ASYCHRONOUS READ CYCLE WE = L = HIGH

# SYNCHRONOUS READ CYCLE WE = HIGH

# WRITE MODE (Cont'd)

The WRITE cycle is initiated by the WE pulse going low provided that  $\overline{\text{CS}}$  is also low. The leading edge of the WE pulse is used to latch the status of the address <u>bus.</u> CS if active (low) will also be latched. NOTE: WE is gated by CS. If CS goes low after WE, the Write Cycle will be initiated by CS, and all timing will be referenced to that edge. CS and the Addresses will then be latched, and the cycle must be terminated by WE going high. The output bus if not already disabled will go to the high Z state tWEZ after WE. The latch signal, if at a logic high, will have no impact on the WRITE cycle. If latch is brought from a logic high to low prior to WE going active then the address inputs and CS will be latched. NOTE: The Latch control (L) will latch CS independent of the state, whereas WE will latch CS only when in the low state. Once latched. CS and the address inputs may be removed after the required hold times have been met.

Data in must be valid tDSW prior to the low-to-high transition of WE. The Data in lines must remain stable for tDHW after WE goes inactive. The write control of the MK 4118 disables the data out buffers during the write cycle; however, output enable (OE) should be used to disable the data out buffers to prevent bus contention between the input data and data that would be output upon completion of the write cycle.

#### READ/MODIFY/WRITE CYCLE

The MK4118 READ/MODIFY/WRITE cycle is merely a combination of the READ and WRITE cycle operations. The asynchronous or synchronous READ cycle may be combined with the WRITE operation. The status of DATA OUT bus will follow the operation outlined in the READ MODE or WRITE MODE.